Desenvolvimento de PCB

Use a estratégia de teste correta no início do projeto de PCB

01/12/2021

Autor / editor: Dirk Müller * / Gerd Kucera

Duas tendências da eletrônica têm influência decisiva na estratégia de teste de placas de circuito impresso: a miniaturização e o aumento das taxas de dados. Isso significa que a testabilidade do PCB é uma questão fundamental.

Empresas do tema

FlowCAD EDA Software Vertriebs GmbH

Sistemas SPEA para eletrônica profissional e automação GmbH

NCAB Group Germany GmbH

Imagem 1: Atenção! O conceito de teste também inclui cabos que são colocados exclusivamente em camadas internas no teste?

(Imagem: FlowCAD)

O teste de PCB pode representar até um quarto do custo total de fabricação de produtos eletrônicos. O planejamento no início do processo de desenvolvimento de PCB permite que esses custos sejam minimizados. As linhas nas camadas internas do PCB também devem ser levadas em consideração no conceito de teste obrigatório.

A miniaturização contínua de produtos finais com placas de circuito cada vez menores, componentes menores e restrições de posicionamento mais rígidas está levando a densidades de embalagens eletrônicas mais altas e à integração de outras tecnologias no design. As vias que percorrem toda a PCB são realizadas como vias de laser cegas e enterradas com um diâmetro muito menor.

Estruturas rígido-flexíveis substituem plugues e conexões de cabos. Os componentes são colocados como componentes embutidos nas camadas internas da placa de circuito impresso. Devido ao nível de tensão reduzido da transmissão de sinal moderno para cerca de 1 V e uma técnica de gravação mais precisa na produção de placas de circuito impresso, as larguras da estrutura das trilhas do condutor e suas distâncias também são reduzidas.

À medida que as taxas de dados aumentam, os regulamentos para uma determinada qualidade de sinal na placa de circuito impresso tornam-se mais complexos e restritivos. Os níveis de tensão e também os valores absolutos de tensão para tolerâncias continuam diminuindo. Existem mais regras de projeto a serem consideradas ao estabelecer as linhas de sinal. Para evitar saltos de impedância como fonte de problemas de SI, os traços podem ter apenas uma largura constante e um certo espaçamento para sinais diferenciais.

Se não houver espaço suficiente para pontos de teste

Tudo isso significa que não há mais espaço para pontos de teste em nenhum dos lados de uma placa de circuito impresso, ou o uso de pontos de teste não é permitido. Alguns projetistas tentaram usar stubs para mover os pontos de teste próximos aos componentes para que eles não fiquem mais cobertos pelo alojamento do componente. Outros projetistas colocaram os pontos de teste diretamente nas linhas ou tentaram ramificar um ponto de teste da linha de sinal com stubs. Mas todas essas tentativas têm efeitos negativos na qualidade do sinal com tempos de subida mais acentuados dos sinais ou componentes de frequência mais alta. Eles levam a saltos de impedância e, portanto, a reflexões nas linhas, ou os stubs agem como uma antena para esse sinal. Uma matriz de pontos de teste em um endereço e barramento de dados também afeta as impedâncias das linhas do barramento.

Os PCBs rígidos flexíveis têm muitas vantagens, no entanto, a capacidade de teste desse tipo de PCB é pior em comparação com as soluções tradicionais. Com construções rígido-flexíveis, as opções de contato para o teste são reduzidas devido aos plugues que foram racionalizados. A área flexível é frequentemente excluída como superfície de contato por um revestimento protetor e, portanto, excluída para pontos de teste. Para vias na transição da área rígida para a flexível, áreas especiais de bloqueio, chamadas de keep outs, dificultam as coisas. Eles reduzem ainda mais as oportunidades de aplicação de pontos de teste.

O grande problema da alta densidade de integração

Devido a densidades de integração mais altas nos componentes, o número de pinos nesses componentes também aumenta. São cada vez mais os sinais que vêm de um BGA e imediatamente mergulham sob o BGA para uma camada interna da placa de circuito impresso, onde são encaminhados para o próximo BGA, onde também reaparecem sob um BGA. Quando equipado, este sinal não é mais acessível do lado de fora. Devido ao grande número de sinais em um BGA, uma linha não pode ser roteada para um ponto de teste fora do contorno do componente para cada sinal, também porque o roteamento de linhas de fita em cada sinal leva a antenas.

Pontos de teste apropriados para os adaptadores de agulha

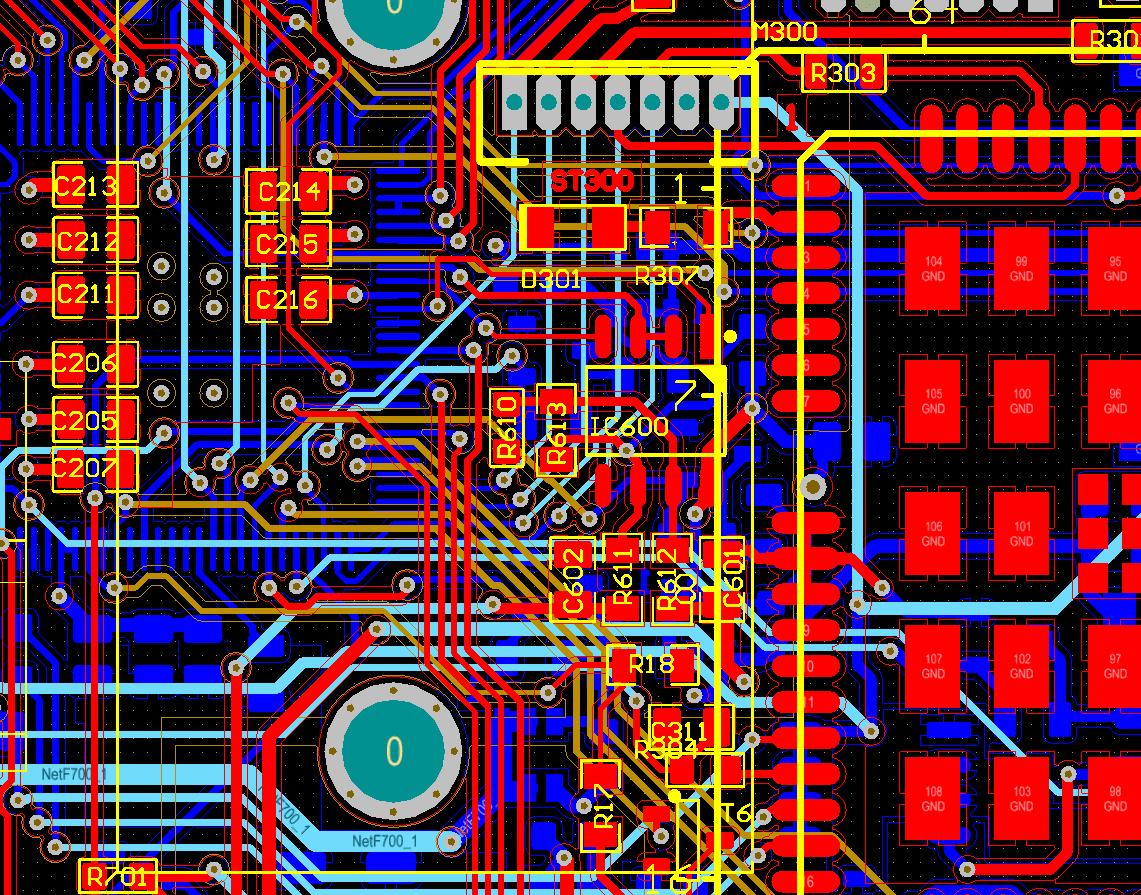

Imagem 2: Estruturas de pontos de teste inadequadas para sinais rápidos na camada superior.

(Imagem: FlowCAD)

Para um teste com adaptadores de agulha, resta apenas o teste no estado não equipado em uma placa nua. Pontos de teste para agulhas de teste podem ser colocados em pontos de teste extras ou vias sem um revestimento protetor. No entanto, isso se aplica apenas a placas de circuito com sinais lentos. Uma via é adequada para teste. No entanto, se sinais rápidos forem posteriormente transmitidos através desta linha durante a operação, então este revestimento de orifício passante é uma antena. O comprimento de uma via de cima para baixo já é muito longo para sinais na faixa de Gbit. Um ponto de teste pode possivelmente ser roteado da primeira camada interna para a camada superior por meio de uma microvia cega.

Embora colocar um ponto de teste do lado de fora pareça um truque inteligente à primeira vista, a velocidade do sinal e, portanto, o comprimento máximo do stub devem ser verificados. Dependendo do tempo de subida do sinal, a via interna da placa, que é contatada de um lado, torna-se uma antena que emite sinais ou recebe interferências.

O teste da placa de circuito via interface JTAG

Imagem 3: Via curta e longa (ponta) para conectar pontos de teste em camadas internas.

(Imagem: FlowCAD)

Os fabricantes de componentes já abordaram os problemas conhecidos do teste. Os fabricantes de BGAs começaram porque o problema de sinais submersos sob o BGA tornou-se aparente aqui. Eles anexaram uma interface JTAG ao BGA, com a qual o BGA pode ser alternado para um autoteste externo. Este pequeno circuito de teste, integrado no silício do chip, pode alternar entre todos os pinos e a função real no IC.

Dois circuitos integrados podem se comunicar entre si através da interface JTAG e executar um programa de teste. Para fazer isso, uma conexão elétrica de teste é feita do pino de medição da interface JTAG a um pino do BGA. A mesma coisa acontece no segundo BGA, completando um circuito entre os dois pinos de sentido JTAG e a conexão entre os BGAs. Com esta técnica, não apenas uma interface JTAG pode ser usada para verificar se uma conexão elétrica está presente, mas também a função dos componentes que estão conectados entre os BGAs, ou o valor de uma resistência em série também pode ser medido.

Dependendo do circuito, uma alta cobertura de teste já pode ser alcançada com o Boundary Scan. Embora as linhas de ônibus JTAG também exijam espaço, elas podem ser colocadas em camadas internas e, portanto, não impedem a necessidade de miniaturização. A interface JTAG oferece outra vantagem, pois também pode ser usada para programar dispositivos.

A estratégia de teste adequada é encontrada rapidamente

Com a estratégia de teste certa, o desenvolvedor pode decidir antecipadamente quais redes serão testadas e quais redes podem permanecer sem teste. Ele pode tomar essa decisão em um estágio inicial, juntamente com o layout e a produção. Se as redes que precisam ser testadas posteriormente já estiverem definidas no diagrama de circuito, uma estratégia comum para testabilidade pode ser elaborada. Devem ser levados em consideração os regulamentos de teste, que especificam, por exemplo, o número de pontos de teste em uma rede (0, 1 ou 2) e as distâncias máximas que os pontos de teste podem ter dos pinos de conexão. Essas regras geralmente podem ser atribuídas rapidamente a um grupo de redes no Gerenciador de restrições.

Reduzir pontos de teste pode ser uma alternativa

Se a montagem contém sinais que não podem ser alcançados por meio de agulhas de teste, a estratégia deve ser invertida. Se a varredura de limite for usada, deve-se tentar reduzir o máximo possível de pontos de teste e testar os sinais usando métodos de teste de varredura de limite e, ao mesmo tempo, melhorar a qualidade do sinal do circuito. No geral, é necessário um equilíbrio significativo entre os diferentes métodos de teste.

Figura 4: Use o DFT Assistant do XJTAG para registrar e gerenciar a cobertura de teste dos diferentes métodos de teste no esquema.

(Imagem: FlowCAD)

O software DFT-Assistant gratuito do XJTAG detecta automaticamente quais sinais são acessíveis para um teste JTAG em todo o esquema. Este software da XJTAG interage com ferramentas EDA populares, como OrCAD e Allegro da Cadence, bem como ferramentas da Mentor, Altium e Zuken.

Os resultados são exibidos como redes coloridas no esquema. O usuário pode escolher entre as categorias de Boundary Scan "leitura, escrita, fonte de alimentação/terra e redes sem acesso JTAG no esquema". A cobertura do teste é claramente exibida no OrCAD Capture, por exemplo, e pode ser facilmente documentada mostrando e ocultando no diagrama de circuito.

Você também pode ler este artigo na revista comercial ELEKTRONIKPRAXIS edição 02/01/2021 (Baixar PDF)

Redes que não podem ser alcançadas com JTAG requerem diferentes estratégias de teste ou o circuito deve ser redesenhado. Há uma compensação entre os procedimentos, etapas e tempos de teste, o espaço disponível no PCB e o impacto na qualidade do sinal. Portanto, é aconselhável planejar a testabilidade junto com o layouter de PCB e a produção no início da fase de desenvolvimento, a fim de encontrar o ideal.

* Dirk Müller é diretor administrativo da FlowCAD em Feldkirchen.

Arquivos de artigos e links de artigos

Link:

Boundery Scan e outras ferramentas do FlowCAD

(ID:47020617)