Leiterplatten-Entwicklung

Im PCB Design die richtige Teststrategie frühzeitig anwenden

12.01.2021

Autor / Redakteur: Dirk Müller * / Gerd Kucera

Auf die Teststrategie für Leiterplatten haben zwei Trends der Elektronik entscheidenden Einfluss: Miniaturisierung und steigende Datenraten. Damit ist die Testbarkeit der PCB ein zentrales Thema.

Firmen zum Thema

FlowCAD EDA-Software Vertriebs GmbH

SPEA Systeme f. Professionelle Elektronik und Automation GmbH

NCAB Group Germany GmbH

Bild 1: Achtung! Sind im Testkonzept auch Leitungen, die ausschließlich auf Innenlagen verlegt sind, in der Prüfung berücksichtigt?

(Bild: FlowCAD)

Der Test von Leiterplatten kann bis zu einem Viertel der gesamten Herstellungskosten der Elektronik ausmachen. Frühzeitiges Planen im PCB-Entwicklungsprozess ermöglicht die Minimierung dieser Kosten. Im obligatorischen Testkonzept müssen auch die Leitungen auf den PCB-Innenlagen unbedingt berücksichtigt werden.

Die fortwährende Miniaturisierung von Endprodukten mit immer kleineren Leiterplatten, kleineren Bauteilen und engeren Platzierungsvorgaben führt zu einer höheren Packungsdichte der Elektronik und dazu, dass andere Technologien in das Design integriert werden. Durchkontaktierungen, die durch die ganze Leiterplatte gehen, werden als blind und burried Laser-Vias mit viel kleinerem Durchmesser realisiert.

Starr-flexible Aufbauten ersetzen Stecker und Kabelverbindungen. Bauteile werden als Embedded Components auf die Innenlagen in der Leiterplatte platziert. Durch die gesunkenen Spannungspegel moderner Signalübertragung auf etwa 1 V und eine präzisere Ätztechnik in der Leiterplattenfertigung verringern sich darüber hinaus die Strukturbreiten der Leiterbahnen und deren Abstände.

Mit steigenden Datenraten werden die Vorschriften für eine bestimmte Signalqualität auf der Leiterplatte komplexer und restriktiver. Die Spannungspegel und auch die absoluten Spannungswerte für Toleranzen sinken weiter. Beim Verlegen der Signalleitungen sind mehr Design-Regeln zu berücksichtigen. Um Impedanzsprünge als Quelle für SI-Probleme zu vermeiden, dürfen Leiterbahnen nur noch eine konstante Breite und bei differentiellen Signalen einen bestimmten Abstand haben.

Wenn der Platz für Testpunkte fehlt

All das führt dazu, dass auf beiden Außenseiten einer Leiterplatte kein Platz mehr für Testpunkte bleibt bzw. die Verwendung von Testpunkten nicht erlaubt ist. Einige Designer versuchten mit Stubs die Testpunkte neben die Bauteile zu verlegen, sodass sie nicht mehr vom Gehäuse der Bauteile verdeckt werden. Andere Designer platzierten die Testpunkte direkt auf die Leitungen oder versuchten mit Stubs einen Testpunkt von der Signalleitung abzuzweigen. Aber alle diese Versuche haben bei steileren Anstiegszeiten der Signale bzw. höheren Frequenzanteilen negative Auswirkungen auf die Signalqualität. Sie führen zu Impedanzsprüngen und damit zu Reflexionen auf den Leitungen, oder die Stubs wirken wie eine Antenne für dieses Signal. Auch ein Feld von Testpunkten auf einem Adress- und Datenbus hat Auswirkungen auf die Impedanzen der Busleitungen.

Starr-flexible Leiterplatten weisen viele Vorteile auf, jedoch ist die Testbarkeit bei dieser PCB-Art schlechter im Vergleich zu traditionellen Lösungen. Bei starr-flexiblen Konstruktionen verringern sich die Kontaktierungsmöglichkeiten für den Test durch die wegrationalisierten Stecker. Der flexible Bereich ist oftmals durch einen Schutzlack als Kontaktfläche ausgenommen und somit für Testpunkte ausgeschlossen. Für Durchkontaktierungen im Übergang vom starren zum flexiblen Bereich kommen besondere Sperrflächen, Keep Outs genannt, erschwerend hinzu. Sie reduzieren die Möglichkeiten zum Aufbringen von Testpunkten noch weiter.

Das große Problem der hohen Integrationsdichte

Durch höhere Integrationsdichten bei Bauteilen steigt auch die Anzahl der Pins an diesen Bauteilen. Vermehrt gibt es Signale, die aus einem BGA kommen und sofort unter dem BGA in eine Innenlage der Leiterplatte abtauchen, dort bis zum nächsten BGA verlegt werden, wo sie ebenfalls unter einem BGA wieder auftauchen. Im bestückten Zustand ist dieses Signal von außen nicht mehr zugänglich. Aufgrund der Vielzahl von Signalen unter einem BGA kann auch nicht für jedes Signal eine Leitung zu einem Testpunkt außerhalb der Bauteilkontur geführt werden, auch weil das Herausführen von Stegleitungen an jedem Signal zu Antennen führt.

Geeignete Testpunkte für die Nadeladapter

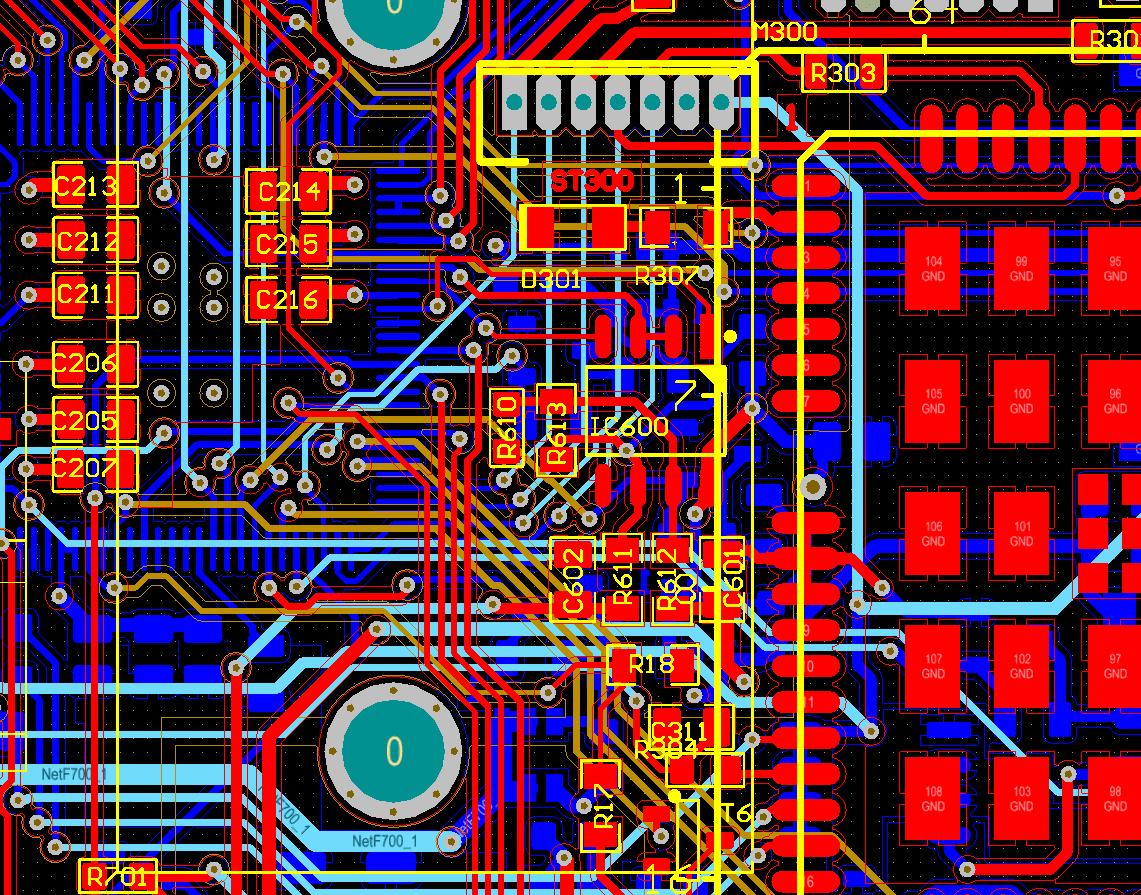

Bild 2: Ungeeignete Testpunktstrukturen für schnelle Signale auf der Top-Lage.

(Bild: FlowCAD)

Für einen Test mit Nadeladaptern bleibt also nur der Test im unbestückten Zustand auf einem Bareboard. Testpunkte für Testnadeln können auf extra Testpunkten oder Durchkontaktierungen ohne Schutzlack platziert sein. Dies gilt aber nur für Leiterplatten mit langsamen Signalen. Für das Testen ist eine Durchkontaktierung geeignet. Werden aber später im Betrieb über diese Leitung schnelle Signale übertragen, dann ist diese Durchkontaktierung eine Antenne. Die Länge einer Durchkontaktierung von Top zu Bottom ist für Signale im GBit-Bereich bereits zu lang. Möglicherweise kann ein Testpunkt über ein blindes Microvia von der ersten Innenlage zur Top-Lage geführt werden.

Auch wenn es auf den ersten Blick wie ein cleverer Trick aussieht, einen Testpunkt auf der weit entfernten Außenseite zu platzieren, sollte die Signalgeschwindigkeit und damit die maximale Länge des Stubs überprüft werden. Je nach Anstiegszeit des Signals wird aus dem einseitig kontaktiertem Via im Inneren der Leiterplatte eine Antenne, die Signale abstrahlt oder Störungen empfängt.

Der Leiterplattentest über die JTAG-Schnittstelle

Bild 3: Kurzes und langes Via (Stub) zum Anschließen von Testpunkten auf Innenlagen.

(Bild: FlowCAD)

Die bekannten Probleme des Tests haben die Bauteil-Hersteller bereits adressiert. Begonnen haben die Hersteller von BGAs, da sich hier zuerst das Problem von abtauchenden Signalen unter dem BGA zeigte. Sie brachten eine JTAG-Schnittstelle am BGA an, mit der das BGA von außen in einen Selbsttest geschaltet werden kann. Diese kleine Testschaltung, eingebunden auf dem Silizium des Chips, kann sich zwischen alle Pins und der eigentlichen Funktion auf dem IC schalten.

Zwei integrierte Schaltkreise können über die JTAG-Schnittstelle miteinander kommunizieren und ein Testprogramm ablaufen lassen. Dazu wird eine elektrische Testverbindung vom Mess-Pin der JTAG-Schnittstelle zu einem Pin des BGAs hergestellt. Das Gleiche passiert auf dem zweiten BGA, sodass ein Stromkreis zwischen den beiden JTAG-Mess-Pins und der Verbindung zwischen den BGAs geschlossen wird. Mit dieser Technik lässt sich über eine JTAG-Schnittstelle nicht nur prüfen, ob eine elektrische Verbindung vorhanden ist, sondern auch die Funktion von Bauteilen testen, die zwischen den BGAs angeschlossen sind, oder darüber hinaus der Wert eines Serienwiderstands messen.

Je nach Schaltung kann mit Boundary Scan bereits eine hohe Testabdeckung erreicht werden. Die JTAG-Busleitungen benötigen zwar auch Platz, können aber auf Innenlagen verlegt werden und stehen damit der Anforderung nach Miniaturisierung nicht im Weg. Die JTAG-Schnittstelle bietet noch einen weiteren Vorteil, da sie auch zum Programmieren von Bauteilen verwendet werden kann.

Die geeignete Teststrategie ist schnell gefunden

Mit der geeigneten Teststrategie kann der Entwickler früh gezielt entscheiden, wie welche Netze getestet werden und welche Netze gegebenenfalls ungetestet bleiben dürfen. Diese Entscheidung kann er frühzeitig zusammen mit dem Layout und der Fertigung treffen. Wenn bereits im Stromlaufplan die Netze festgelegt werden, an denen später getestet werden muss, lässt sich eine gemeinsame Strategie für die Testbarkeit erarbeiten. Dabei sind die Testvorschriften zu berücksichtigen, die beispielsweise die Anzahl der Testpunkte an einem Netz spezifizieren (0, 1 oder 2) und welche maximalen Abstände die Testpunkte von den Anschlusspins haben dürfen. Solche Regeln können üblicherweise im Constraint Manager schnell einer Gruppe von Netzen zugewiesen werden.

Testpunkte reduzieren kann eine Alternative sein

Zeigt sich, dass die Baugruppe Signale enthält, die nicht über Testnadeln zu erreichen sind, dann sollte sich die Strategie umkehren. Wenn Boundary Scan eingesetzt wird, dann sollte man versuchen, möglichst viele Testpunkte zu reduzieren und die Signale über Boundary-Scan-Testverfahren zu prüfen sowie gleichzeitig die Signalqualität der Schaltung zu verbessern. Es bedarf insgesamt einer sinnvollen Abwägung zwischen den unterschiedlichen Testverfahren.

Bild 4: Mit dem DFT-Assistant von XJTAG die Testabdeckung der unterschiedlichen Testmethoden im Schaltplan erfassen und verwalten.

(Bild: FlowCAD)

Mit der kostenlosen Software DFT-Assistant von XJTAG wird automatisch über den gesamten Schaltplan erkannt, welche Signale für einen JTAG-Test zugänglich sind. Diese Software von XJTAG spielt mit den gängigen EDA Tools wie OrCAD und Allegro von Cadence sowie den Tools von Mentor, Altium und Zuken zusammen.

Die Ergebnisse werden als farblich eingefärbte Netze im Schaltplan angezeigt. Der Anwender kann wahlweise zwischen den Boundary Scan Kategorien „Lesen, Schreiben, Stromversorgung/Masse und Netze ohne JTAG-Zugriff im Schaltplan“ wählen. Die Test-Coverage ist beispielsweise in OrCAD Capture übersichtlich dargestellt und durch das Ein- und Ausblenden im Schaltplan kann leicht dokumentiert werden.

Diesen Beitrag lesen Sie auch in der Fachzeitschrift ELEKTRONIKPRAXIS Ausgabe 1/2 / 2021 (Download PDF)

Nicht mit JTAG erreichbare Netze benötigen andere Teststrategien oder die Schaltung muss umgeplant werden. Es gilt abzuwägen zwischen den Verfahren, Schritten und Zeiten für den Test sowie dem vorhandenen Platz auf der PCB und den Auswirkungen auf die Signalqualität. Daher ist es ratsam, bereits früh in der Phase der Entwicklung die Testbarkeit gemeinsam mit dem PCB Layouter und der Fertigung zu planen, um das Optimum zu finden.

* Dirk Müller ist Geschäftsführer bei FlowCAD in Feldkirchen..

Artikelfiles und Artikellinks

Link:

Boundery Scan und andere Tools von FlowCAD

(ID:47020617)